SPECIFICATIONS AND FEATURES

DATASHEET

WWW.UNICORE.COM

# UFirebird-UC6226 GNSS Positioning Chip

Copyright© 2009-2024, Unicore Communications, Inc. Data subject to change without notice.

# **Revision History**

| Version  | Revision History                                              | Date        |

|----------|---------------------------------------------------------------|-------------|

| Ver. 1.0 | First Edition                                                 | Aug. 2017   |

| Ver. 2.0 | Add WLCSP                                                     | April. 2019 |

| R3.0     | Two options of VDDIO input voltage are clarified in chapter   | Oct. 2019   |

|          | 10.4                                                          |             |

| R3.1     | Update the Copyright time                                     | Apr. 2020   |

| R3.2     | Align the grade rules                                         | Apr. 2020   |

| R3.3     | Add the footnote of CEP                                       | Oct. 2020   |

| R3.4     | Update the voltage of V_BCKP, VDD_IO, and the V_DCDC_IN       | Oct. 2021   |

|          | current, etc.; Editorial modifications; Add reflow soldering, |             |

|          | ESD standard, and the requirement for voltage ripple;         |             |

|          | Add the requirement for RTC_I pin when RTC is not used        |             |

| R3.5     | Modify the description of TCXO and crystal                    | Nov. 2021   |

| R3.6     | 3.6 Delete Sensor Hub and SPI flash in the system block       |             |

|          | diagram; Add the explanation of SPI in section 3.1.2          |             |

| R3.7     | Update the parameters of VDD_IO                               | Mar. 2022   |

| R3.8     | Modify the requirement for V_BCKP, RTC_I and RTC_O            | Nov. 2022   |

|          | when RTC is not used.                                         |             |

|          | Add PPS output current in Table 7-3.                          |             |

|          | Update the sensitivity parameters in Table 1-1.               |             |

| R3.9     | Update the typical current in Table 7-7;                      | Aug. 2023   |

|          | Add details about the reset pin in section 5.3;               |             |

|          | Add definition of pin0 in Table 6-1                           |             |

| R3.10    | Chapter 8: separate the mechanical drawings for               | Jul. 2024   |

|          | UC6226NIS and UC6226NAS                                       |             |

#### Legal right notice

This manual provides information and details on the products of Unicore Communication, Inc. ("Unicore") referred to herein.

All rights, title and interest to this document and the information such as data, designs, layouts contained in this manual are fully reserved, including but not limited to the copyrights, patents, trademarks and other proprietary rights as relevant governing laws may grant, and such rights may evolve and be approved, registered or granted from the whole information aforesaid or any part(s) of it or any combination of those parts.

Unicore holds the trademarks of "和芯星通", "UNICORECOMM", "Unicore" and other trade name, trademark, icon, logo, brand name and/or service mark of Unicore products or their product serial referred to in this manual (collectively "Unicore Trademarks").

This manual or any part of it, shall not be deemed as, either expressly, implied, by estoppel or any other form, the granting or transferring of Unicore rights and/or interests (including but not limited to the aforementioned trademark rights), in whole or in part.

#### Disclaimer

The information contained in this manual is provided "as is" and is believed to be true and correct at the time of its publication or revision. This manual does not represent, and in any case, shall not be construed as a commitments or warranty on the part of Unicore with respect to the fitness for a particular purpose/use, the accuracy, reliability and correctness of the information contained herein.

Information, such as product specifications, descriptions, features and user guide in this manual, are subject to change by Unicore at any time without prior notice, which may not be completely consistent with such information of the specific product you purchase.

Should you purchase our product and encounter any inconsistency, please contact us or our local authorized distributor for the most up-to-date version of this manual along with any addenda or corrigenda.

# Foreword

This datasheet offers you information in the features of the hardware, the installation, specification and use of UNICORECOMM UC6226 product.

#### Readers it applies to

This datasheet is applied to technicians who know GNSS receivers to some extent but not to the general readers.

# Contents

| 1. | Functional Characteristics |                                 |    |

|----|----------------------------|---------------------------------|----|

|    | 1.1.                       | Overview                        | 1  |

|    | 1.2.                       | Features                        | 2  |

|    | 1.3.                       | Performance Specifications      | 2  |

|    | 1.4.                       | System Block Diagram            | 3  |

|    | 1.5.                       | Satellite Navigation Systems    | 3  |

|    |                            | 1.5.1. GPS                      | 4  |

|    |                            | 1.5.2. GLONASS                  | 4  |

|    |                            | 1.5.3. BDS                      | 4  |

|    |                            | 1.5.4. Galileo                  | 4  |

|    | 1.6.                       | Protocols and Interfaces        | 4  |

|    |                            | 1.6.1. Terms and Abbreviations  | 4  |

| 2. | RF S                       | ubsystem                        | 6  |

|    | 2.1.                       | LNA                             | 6  |

|    | 2.2.                       | Gain Block                      | 6  |

|    | 2.3.                       | Mixer                           | 6  |

|    | 2.4.                       | I/Q Low-Pass Filter (LPF)       | 7  |

|    | 2.5.                       | PGA                             | 7  |

|    | 2.6.                       | ADC                             | 7  |

| 3. | Base                       | eband Subsystem                 | 8  |

|    | 3.1.                       | Interfaces                      |    |

|    |                            | 3.1.1. UART                     | 8  |

|    |                            | 3.1.2. SPI                      | 8  |

|    | 3.2.                       | PI0                             | 8  |

|    | 3.3.                       | Watchdog                        | 10 |

|    | 3.4.                       | Timer Counter                   | 10 |

|    | 3.5.                       | Clock                           | 10 |

|    |                            | 3.5.1. TCXO                     | 10 |

|    |                            | 3.5.2. PLL                      | 10 |

|    |                            | 3.5.3. RTC                      | 10 |

|    |                            | 3.5.4. Clock Source Combination | 11 |

| 3.6.                             | Power Management Unit (PMU)                                                                                                                                                        | 12                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |  |  |

|----------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

|                                  | 3.6.1. DC/DC Converter                                                                                                                                                             | 13                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |  |  |

| Opera                            | Dperating Modes                                                                                                                                                                    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |  |  |

| 4.1.                             | Continuous Tracking Mode                                                                                                                                                           | 14                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |  |  |

| 4.2.                             | Sleep Mode                                                                                                                                                                         | 14                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |  |  |

| Syste                            | em Configuration                                                                                                                                                                   | 15                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |  |  |

| 5.1.                             | Configure the Communication Interface                                                                                                                                              | 15                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |  |  |

| 5.2.                             | Configuration Pins                                                                                                                                                                 | 15                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |  |  |

| 5.3.                             | System Reset                                                                                                                                                                       | 15                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |  |  |

| 5.4.                             | Power on Sequence                                                                                                                                                                  | 16                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |  |  |

|                                  | 5.4.1. DC/DC Power-on and Sequence                                                                                                                                                 | 17                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |  |  |

|                                  | 5.4.2. DC/DC Bypass Power-on and Sequence                                                                                                                                          | 18                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |  |  |

|                                  |                                                                                                                                                                                    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |  |  |

| Pin D                            | efinitions                                                                                                                                                                         | 20                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |  |  |

| 6.1.                             | Pin Distribution                                                                                                                                                                   | 20                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |  |  |

| 6.2.                             | Pin Description                                                                                                                                                                    | 21                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |  |  |

| Elect                            | rical Specifications                                                                                                                                                               | 23                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |  |  |

| 7.1.                             | Maximum Absolute Rating                                                                                                                                                            | 23                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |  |  |

| 7.2.                             | Working Conditions                                                                                                                                                                 | 24                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |  |  |

|                                  | 7.2.1. DC Electrical Characteristics                                                                                                                                               | 24                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |  |  |

|                                  | 7.2.2. Analog Parameters                                                                                                                                                           | 25                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |  |  |

|                                  |                                                                                                                                                                                    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |  |  |

|                                  | -                                                                                                                                                                                  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |  |  |

| 7.3.                             | Reference Power Requirements                                                                                                                                                       | 27                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |  |  |

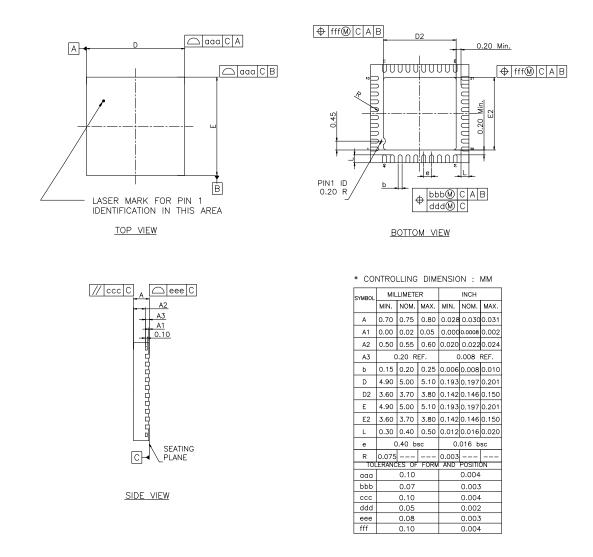

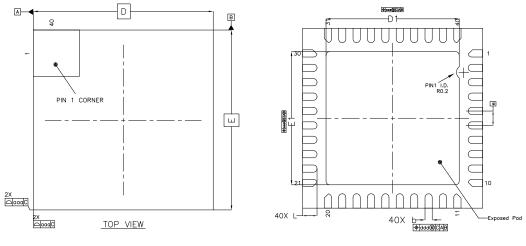

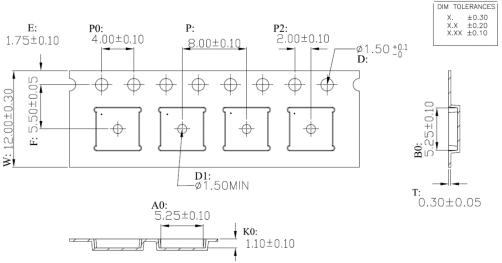

| Mech                             | nanical Specifications                                                                                                                                                             | . 28                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |  |  |

| 8.1.                             | UC6226NIS                                                                                                                                                                          | 28                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |  |  |

| 8.2.                             | UC6226NAS                                                                                                                                                                          | 29                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |  |  |

| Relia                            | bility Test and Certificate                                                                                                                                                        | . 30                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |  |  |

| 9.1.                             | Reliability Test                                                                                                                                                                   | 30                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |  |  |

| 9.2.                             | Certificate                                                                                                                                                                        | 30                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |  |  |

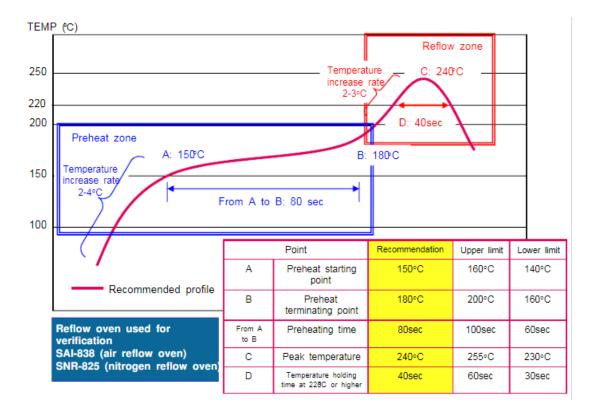

| Reflow Soldering                 |                                                                                                                                                                                    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |  |  |

| Product Appearance and Packaging |                                                                                                                                                                                    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |  |  |

|                                  | Opera<br>4.1.<br>4.2.<br>Syste<br>5.1.<br>5.2.<br>5.3.<br>5.4.<br>Pin D<br>6.1.<br>6.2.<br>Elect<br>7.1.<br>7.2.<br>7.3.<br>Mech<br>8.1.<br>8.2.<br>Relia<br>9.1.<br>9.2.<br>Reflo | 3.6.1. DC/DC Converter.         Operating Modes.         4.1. Continuous Tracking Mode.         4.2. Sleep Mode         System Configuration         5.1. Configure the Communication Interface         5.2. Configuration Pins.         5.3. System Reset.         5.4. Power on Sequence.         5.4.1. DC/DC Power-on and Sequence.         5.4.2. DC/DC Bypass Power-on and Sequence.         5.4.3. Power on Sequence for Backup Region         Pin Definitions         6.1. Pin Distribution.         6.2. Pin Description         Electrical Specifications         7.1. Maximum Absolute Rating.         7.2. Working Conditions         7.2.1. DC Electrical Characteristics.         7.2.2. Analog Parameters         7.2.3. RF Parameters.         7.2.4. Current Consumption         7.3. Reference Power Requirements         Mechanical Specifications         8.1. UC6226NIS         8.2. UC6226NAS         Reliability Test and Certificate         9.1. Reliability Test         9.2. Certificate         Reflow Soldering |  |  |

|     | 11.1. | Appearance | . 32 |

|-----|-------|------------|------|

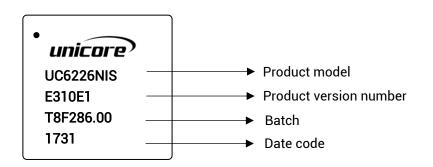

|     | 11.2. | Label      | . 32 |

|     | 11.3. | Packaging  | . 33 |

| 12. | Orde  | ring Codes | 34   |

# 1. Functional Characteristics

# 1.1. Overview

Figure 1-1 UFirebird-UC6226 Chip

UNICORECOMM UFirebird<sup>™</sup> (UC6226) is designed with 28 nm process and efficient PMU, features low power consumption and ultimate compact size, which significantly increase the battery life of user equipment.

UC6226 is suitable for global applications, supports GPS, GLONASS, BDS, Galileo and multisystem positioning, as well as supports a variety of SBAS signal reception processing, thus providing users with fast and accurate high-performance positioning experience.

UC6226 can connect with the gyroscope, accelerometer, and other sensors to realize fusion positioning. With the accurate scenes and pattern recognition, in the harsh signal environment, UC6226 can still ensure fast and accurate positioning effect, and significantly reduce the average operating power consumption, substantially increase the standby time of devices, such as mobile phones, wearing devices and Internet of Things devices.

What's more, UC6226 has adopted the high integration design, and the chip has provided built-in DC/DC, LDO, LNA and RTC, etc. With the simple peripheral devices, it can achieve a complete GNSS receiver function, which can significantly reduce the PCB area and save hardware costs for users.

UC6226 QFN40 package is AEC-Q100-Compliant, is compatible with mainstream package.

## 1.2. Features

UC6226 has the following features:

- Positioning engine features

- > 64-channel simultaneous tracking

- Less than 1 second hot start time

- > -147 dBm cold start sensitivity, -160 dBm tracking sensitivity

- > Up to 5 Hz data update rate

- Supports GPS, BDS, GLONASS and Galileo

- Supports 26 MHz TCXO

- Supports external 32.768 kHz crystal

- Built-in DC/DC and power management unit

- Supports ROM built-in firmware and Flash expansion firmware

- Automotive grade 5.0 mm x 5.0 mm QFN40 package, 0.4 mm pitch

# 1.3. Performance Specifications

GNSS performance specifications of UC6226 are as follows:

#### Table 1-1 UC6226 GNSS performance

| Item                                  | Description |

|---------------------------------------|-------------|

| Positioning accuracy                  |             |

| Single point positioning <sup>1</sup> | <2.0 m      |

| Velocity accuracy                     | 0.1 m/s     |

| Sensitivity <sup>2</sup>              |             |

|                                       | GNSS        |

| Cold Start <sup>3</sup>               | -147 dBm    |

| Tracking                              | -160 dBm    |

| Hot start                             | -154 dBm    |

| Reacquisition                         | -158 dBm    |

|                                       |             |

<sup>&</sup>lt;sup>1</sup> CEP, 50%

$<sup>^2~</sup>$  The sensitivity index needs C/N0 attain 41dB when the signal strength is -130dBm ~

<sup>&</sup>lt;sup>3</sup> Externally matches LNA to ensure superior performance

| TTFF4              |      |  |

|--------------------|------|--|

| Cold start         | <28s |  |

| AGNSS <sup>5</sup> | <4s  |  |

| Hot start          | <1s  |  |

| Reacquisition      | <1s  |  |

# 1.4. System Block Diagram

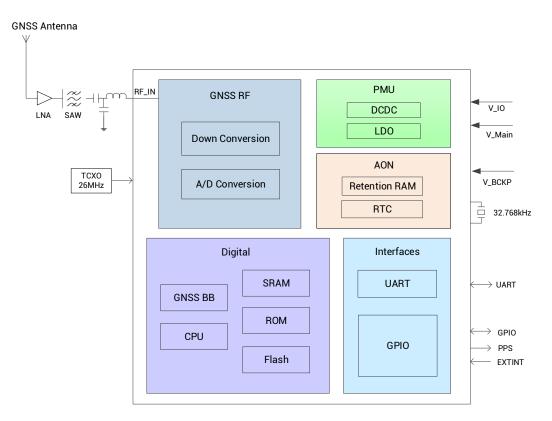

Figure 1-2 UC6226 chip block diagram

# 1.5. Satellite Navigation Systems

UC6226 supports multiple GNSS systems, including GPS, BDS, GLONASS and Galileo. RF uses a broadband design that simultaneously receives and processes satellite signals from multiple satellite systems, including GPS L1, BDS B1, GLONASS L1 and Galileo E1, which can receive or process two or three of them in parallel.

<sup>&</sup>lt;sup>4</sup> Satellite signal strength is up to -130dBm

<sup>&</sup>lt;sup>5</sup> Prompt injection of assisted ephemeris

#### 1.5.1. GPS

The UC6226 can receive and track GPS L1 signal at 1575.42 MHz.

### 1.5.2. GLONASS

UC6226 can receive and track GLONASS L1 signal, the signal frequency is 1602 MHz + k \* 562.5 kHz, k = -7 ~ +6. Users can design GLONASS receivers in compliance with regulatory requirements.

# 1.5.3. BDS

UC6226 can receive and track the BDS satellite navigation system's 1561.098 MHz B1 signal. It can combine with GPS to receive and track the BDS B1 satellite signal, increase the coverage, improve reliability and improve accuracy.

### 1.5.4. Galileo

UC6226 can simultaneously receive and track GPS and Galileo signals, as well as enhance accuracy and coverage.

# 1.6. Protocols and Interfaces

UC6226 data protocol complies with "Unicore Protocol" specification. By default, UC6226 communicates with host device via UART. For the technical parameters of the various protocols, supported communication interfaces and firmware versions, please refer to the *UFirebird\_Standard Positioning Products Protocol Specification* documentation.

# 1.6.1. Terms and Abbreviations

The following table lists the terms and abbreviations involved or used in this document:

| Abbreviations | Complete Description or Name     |

|---------------|----------------------------------|

| A/D           | Analog/Digital                   |

| ADC           | Analog Digital Convertor         |

| AGC           | Automatic Gain Control           |

| AGNSS         | Assisted GNSS                    |

| BB            | Baseband                         |

| DC/DC         | Direct Current to Direct Current |

| DGNSS         | Differential GNSS                |

#### Table 1-2 List of terms and abbreviations

| Abbreviations | Complete Description or Name              |  |  |

|---------------|-------------------------------------------|--|--|

| Galileo       | Galileo Navigation Satellite System       |  |  |

| GLONASS       | Global Navigation Satellite System        |  |  |

| GNSS          | Global Navigation Satellite System        |  |  |

| GPS           | Global Positioning System                 |  |  |

| LDO           | Low DropOut regulator                     |  |  |

| LNA           | Low Noise Amplifier                       |  |  |

| PGA           | Programmable Gain Amplifier               |  |  |

| PIO           | Programming Input/Output                  |  |  |

| PLL           | Phase Locked Loop                         |  |  |

| PMU           | Power Management Unit                     |  |  |

| POR           | Power On Reset                            |  |  |

| RAM           | Random Access Memory                      |  |  |

| RF            | Radio Frequency                           |  |  |

| RTC           | Real-Time Clock                           |  |  |

| SBAS          | Satellite-Based Augmentation System       |  |  |

| SAW           | Surface Acoustic Wave                     |  |  |

| SPI           | Serial Peripheral Interface               |  |  |

| ТСХО          | Temperature Compensate Crystal Oscillator |  |  |

# 2. RF Subsystem

RF subsystem adopts wideband design. The input signal is centered at about 1575MHz with a 100 MHz band width. The received GNSS signals are amplified by a Low Noise Amplifier (LNA), and then fed to a gain block, which offers further amplification, thus reducing the noise figure requirements for the mixer. The gain block also provides a single-ended to differential conversion.

After the complex down-conversion, the multi-GNSS signals are split up into I and Q channels. Afterwards both channels are I/Q low-pass filtered and amplified by separate Programmable Gain Amplifiers (PGA). The amplified I and Q signals will do the A/D conversion to get 6-bits I/Q digital signals that are then sent to baseband section, where signal processing and final image rejection take place.

# 2.1. LNA

The low noise amplifier (LNA) makes use of a single stage configuration and requires external matching to function satisfactorily. For improved performance, an external LNA should be added, of which the gain range is recommended to be within 17dB~45dB. Moreover, it is necessary to use an external SAW filter to suppress out-of-band interference.

# 2.2. Gain Block

A single stage differential amplifier follows the LNA providing further amplification and conversion from single-ended to differential signaling.

# 2.3. Mixer

UC6226 uses the active I/Q mixer to first convert the multi-GNSS signals to an intermediate frequency. At this stage the signals are split into two similar IF channels. Both channels are further amplified and converted into different GNSS signal band.

# 2.4. I/Q Low-Pass Filter (LPF)

The low-pass filter removes any high-frequency from the desired signal. For single GNSS system signal reception, their cut-off frequency and band width are adjusted lower to reduce power consumption.

# 2.5. PGA

The programmable gain amplifiers (PGA) are used to provide the ADCs with appropriate input IF signals. The PGA gain is automatically looped and adjusted based on the ADC output signal values, providing an automatic gain control (AGC) for the receiver.

PGA gain can be configured as a fixed value via GPIO to improve system's robustness, which is suitable for applications that integrate with mobile communication functions.

# 2.6. ADC

Two 6-bit ADCs are used for A/D conversion in the UC6226. I and Q-branch ADCs output 6bit signals respectively, which then enter into baseband subsystem for processing.

# 3. Baseband Subsystem

# 3.1. Interfaces

The digital I/O of the baseband section is powered by VDD\_IO, and the VDD\_IO level is the same as applied logic voltage level. Without supplying VDD\_IO, the UC6226 will not work.

As the UC6226's selected digital IO does not support anti-current backflush function, IO interface should not be supplied power separately in the case of power down in the actual application. Please see the note in 3.2 for details.

# 3.1.1. UART

The UC6226 makes use of two UART interfaces, UART1 and UART2, which can be used for communication with a host. Both of them support configurable baud rates up to 921600bps.

By default, PIO6/PIO7 corresponds with UART1, which is the main UART port in standard firmware version. The communication interface of the UC6226 can be mapped to a different PIO interface via D\_SEL. PIO6/PIO7 can also be used as an SPI, at which point UART1 will be mapped to PIO15/PIO16. Refer to the note in 3.2 for D\_SEL usage and corresponding communication interface mapping.

UART2 can use PI017/PI018, or PI010/PI012, or PI02/PI03. By default, UART2 will use PI017/PI018 in the standard firmware. UART2 is mainly used for transmitting or debugging auxiliary information.

## 3.1.2. SPI

SPI is reserved and is not supported currently.

# 3.2. PIO

The PIO module may be configured as a GPIO or as the aforementioned communication interface. The following table describes all PIO functions.

#### Table 3-1 PIO functions

| PIO # | Default Function | I/O | Description                                                                                         | Alternate Function    |

|-------|------------------|-----|-----------------------------------------------------------------------------------------------------|-----------------------|

| 0     | GPIO             | I/O | NC                                                                                                  |                       |

| 1     | GPIO             | I/O | NC                                                                                                  |                       |

| 2     | GPIO             | I/O | NC                                                                                                  | TIMEPULSE, UART2 TX   |

| 3     | GPIO             | I/O | NC                                                                                                  | TIMEPULSE, UART2 RX   |

| 4     | GPIO             | I/O | NC                                                                                                  |                       |

| 5     | GPIO             | I/O | NC                                                                                                  |                       |

| 6     | ТХІ              | 0   | UART1 TX (if D_SEL is high at startup)                                                              | GPIO                  |

| 7     | RX1              | I   | UART1 RX (if D_SEL is high at startup)                                                              | GPIO                  |

| 8     | GPIO             | I/O | NC                                                                                                  | SCL                   |

| 9     | GPIO             | 1/0 | NC                                                                                                  | SDA                   |

| 10    | D_SEL            | 1   | Communication interface         selection pin.         This pin forces a pull up by         default |                       |

| 11    | TIMEPULSE        | 0   | 1PPS output                                                                                         | EVENT                 |

| 12    | BOOT_MODE        | I   | Bootstrap mode selection<br>pin.<br>This pin forces a pull up by<br>default                         | UART1 TX,<br>UART2 TX |

| 13    | GPIO             | I   | No function by default EVENT,<br>UART1 CTS,<br>SCL                                                  |                       |

| 14    | No function      | I   | Can be configured as     EVENT,       antenna detection input     ANT_DET                           |                       |

| 15    | ANT_OK           | I   | Antenna status detection ANT_SHORT input                                                            |                       |

| 16    | ANT_OFF          | 0   | Antenna power supplySPD_PULSEcontrol output and outputstate is related to the PIO15statestate       |                       |

| 17    | UART2 RX         | I   | UART2 RX                                                                                            | SCL                   |

| 18    | UART2 TX         | 0   | UART2 TX                                                                                            | UART2 TX              |

|       |                  |     |                                                                                                     | SDA                   |

*As the digital IO selected by UC6226 does not support anti-current backflush function, please pay attention to the following points in development and application:*

1) When VDD\_IO and V\_DCDC\_IN/V\_CORE use the same power supply: users should pay attention to the signal state of host port that communicates with UART and functional ports connected with UC6226 when power down. If host computer wants to control the chip power down, users should first set the ports that connect with UC6226 to high impedance state so as to prevent UC6226 from consuming host computer's power or failing to start up.

*2) In case VDD\_IO and V\_DCDC\_IN/V\_CORE do not use the same power supply, users can cut off V\_DCDC\_IN/V\_CORE power supply to achieve the purpose of chip power-down.*

# 3.3. Watchdog

The UC6226 includes a watchdog timer, which prevents system-lockups caused when the software gets trapped in a deadlock. During normal operation, the firmware resets the watchdog's internal counter at regular intervals before timer overflow occurs.

# 3.4. Timer Counter

The timer counter has one TIMEMARK input and one TIMEPULSE output. TIMEMARK can be input via PIO11, PIO13 or PIO14, but only be input through one of the PIOs. TIMEMARK inputs (routed through EXTINT0 and EXTINT1) is timestamp events relative to GPS time.

TIMEPULSE can be output via PIO2, PIO3 or PIO11, but only one TIMEPULSE can be output at one time. TIMEPULSE outputs generate pulse sequence synchronized with GPS or UTC time grid, time intervals can be configured over a wide frequency range.

# 3.5. Clock

# 3.5.1. TCXO

The UC6226 requires an external 26MHz clock, which can be provided by TCXO, providing reference frequency for RF and baseband PLLs.

### 3.5.2. PLL

The fully integrated, low-power PLL generates the system clock from the 26MHz reference frequencies supplied by TCXO.

## 3.5.3. RTC

The RTC is driven internally by a 32.768 kHz oscillator, which makes use of an external 32.768 kHz crystal.

If the main supply voltage and IO power supply fail and a backup battery is connected to V\_BCKP, the baseband, RF, CPU will switch off, but the RTC still runs providing a timing reference for the receiver. This operating mode is called RTC puncturing mode. Under the RTC puncturing mode, the relevant data are still saved in the Retention RAM.

The RTC puncturing mode is required for GNSS hot start function. If RTC is abnormal, it will affect the performance of hot start.

If Retention RAM and RTC are not used, UC6226 does not require a backup battery, and V\_BCKP has to be connected to VDD\_IO.

The standard firmware supports 32.768 kHz by default. And UC6226 also supports external digital clock signal of 32.768 kHz directly input into the RTC\_I pin to replace the crystal. When the external digital clock signal is used to input RTC\_I, please note that its signal amplitude should be within 0.9 V~1.05 V, otherwise it may cause damage to the components of UC6226.

# 3.5.4. Clock Source Combination

| Main clock input          | RTC clock input               | Description                      |

|---------------------------|-------------------------------|----------------------------------|

| 26MHz TCXO provides clock | 32.768 kHz crystal provides   | Normal use                       |

| connection to XTAL_I      | clock connection to RTC_I and | V_BCKP must be provided by       |

|                           | RTC_O                         | battery to keep RTC running      |

| 26MHz TCXO provides clock | 32.768 kHz external digital   | Normal use                       |

| connection to XTAL_I      | signal to RTC_I               | V_BCKP must be provided by       |

|                           |                               | battery to keep RTC running      |

| 26MHz TCXO provides clock | No clock input                | If you do not use the RTC, then  |

| connection to XTAL_I      |                               | connect RTC_O to ground and      |

|                           |                               | leave RTC_I floating. Under this |

|                           |                               | condition, GNSS hot-start        |

|                           |                               | function is disabled.            |

Table 3-2 clock source combination

For the application of the above clock source combination, the following should be noted in the design:

- When using 26 MHz TCXO, the TCXO can be powered by LDO\_X or external power supply, XTAL\_O should be kept floating.

- When 32.768 kHz external digital signal is used as the RTC clock, its waveform amplitude must be attenuated to 0.9 V<sub>p-p</sub>~1.05 V<sub>p-p</sub>, with its maximum not higher than 1.05 V and the minimum not lower than -0.2 V. The clock drift should between

±0.6 Hz, 20 ppm.

# 3.6. Power Management Unit (PMU)

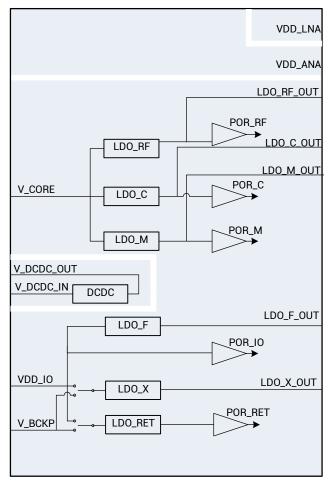

Figure 3-1 Power Management Unit (PMU)

The PMU provides four power domains that are internally generated by LDOs and supervised by several voltage monitors:

> Core

The core domain is the main power domain for the RF and logic inside the chip. Two subsequent LDOs (LDO\_C and LDO\_RF) convert V\_CORE source, and convert V\_CORE to respective voltages, which must be decoupled through LDO\_C\_OUT and LDO\_RF\_OUT pins respectively. The LDO\_C drives the digital logic parts, and the LDO\_RF drives the RF and analog circuits.

LDO\_RF\_OUT does not directly connect or drive RF circuits on-chip. Instead, users should connect it to the VDD\_LNA and VDD\_ANA on PCB to feed the supply into the on-chip RF circuits. It is recommended that users should use noise-resistant connections to improve RF

performance, such as using magnetic beads.

In the case that UC6226 is powered by on-chip DC/DC, voltage range for V\_CORE pin is 1.0V-1.2 V; in DC/DC bypass mode, V\_CORE allows the input voltage range of 1.2V-1.98V.

> 10

The IO power domain is powered by VDD\_IO, including chip IO devices, on-chip Flash, ADC converters and eFuse. The supply voltage of VDD\_IO is 3.3V centered (3.0V – 3.6V). Except IO pads, the other devices are powered by a dedicated LDO\_F to ensure 1.8V supply voltage for on-chip flash, ADC and eFuse. The LDO\_F must be connected with a decoupling capacitor through LDO\_F\_OUT pin.

> Backup

The backup domain runs the RTC section and the Retention RAM. This domain uses the voltage sources of VDD\_IO and V\_BCKP. In case VDD\_IO voltage is inside the normal range, it uses VDD\_IO, otherwise use V\_BCKP. The allowed voltage range of V\_BCKP is 1.65V-3.6V.

➤ TCXO

If using 26MHz TCXO and TCXO is powered by LDO\_X, LDO\_X\_OUT should be connected to the power pin of TCXO and decoupling capacitance. And user can also choose an external power source other than LDO\_X to make TCXO work. Note that if TCXO used as the main clock source, and the clock source is used to drive RTC, do not design the hardware backup function, V\_BCKP can't provide the working current required by TCXO.

### 3.6.1. DC/DC Converter

UC6226 integrates a DC/DC converter, allowing reduced power consumption and cost, especially when using a single supply voltage. To use the chip DC/DC converter, the main power supply must be connected to V\_DCDC\_IN and a capacitor and an inductor must be added to connect V\_DCDC\_OUT to V\_CORE. If a DC/DC converter is not used, connect V\_DCDC\_IN/V\_DCDC\_OUT to V\_CORE.

If a DC/DC converter is used, the allowable input voltage range for V\_DCDC\_IN is from 3.0 V to 3.6 V. If the DC/DC converter is not used, the allowable input voltage range for V\_DCDC\_IN/V\_CORE is from 1.2V to 1.98V. The UC6226 chip will be damaged if power supply exceeds maximum allowable voltage range.

For all power supply, the voltage ripple should not exceed 50mV.

# 4. Operating Modes

# 4.1. Continuous Tracking Mode

Under the full-speed operation mode, the chip's hardware tracking channel will uninterruptedly process satellite signals, to ensure the accuracy of positioning, velocity, and TTFF through high-quality signal acquisition and tracking.

# 4.2. Sleep Mode

The chip is powered off except for the RTC time keeping unit and Backup RAM. Users can easily wake up according to actual needs. Under the sleep mode, the chip operates at very low power levels and can realize hot start quickly after waking up.

# 5. System Configuration

# 5.1. Configure the Communication Interface

The standard communication interface of UC6226 includes two UART serial ports.

# 5.2. Configuration Pins

There are two configuration pins: BOOT\_MODE (PIO12) and D\_SEL (PIO10). When the chip is powered on, the two pins should be pulled up.

# 5.3. System Reset

According to the power structure of UC6226 chip, there are two reset domains: the Core domain and the Backup domain. The Core domain contains all circuits clocked by 26 MHz clock, and Backup domain contains RTC circuits and Retention RAM.

The main RESET controls the reset of the Core domain, and the main RESET domain has the following reset sources:

- POR\_IO is used to detect the IO voltage. When the IO voltage is lower than 2.93 V, the reset signal will be sent to the Core domain;

- POR\_DCDC is used to detect the DC/DC input voltage. In the DC/DC mode, when the DC/DC voltage is less than 3.0 V, the reset signal will be sent to the Core domain; In the DC/DC bypass mode, when the voltage is less than 1.2 V, the reset signal will be sent to the Core domain;

- POR\_C is used to detect the core voltage. When the core voltage is less than 90% of the firmware preset voltage, the reset signal will be sent to the Core domain ;

- POR\_RET is used to detect the voltage of the backup power domain. When the voltage of the backup power domain is less than 0.6V, the reset signal will be sent to the Core domain;

- RESET\_N is the reset pin of the chip. When its level is low and the state keeps for more than 5 milliseconds, the reset signal will be sent to the Core domain;

- > The reset signal of the software system is controlled by the firmware;

➢ Watchdog RESET.

If any of the above reset sources issues a Core domain reset signal, the Core domain will be reset.

The Backup RESET domain has the following reset sources:

- > POR\_RET is used to detect the supply voltage of backup power domain;

- > The RTC RESET signal is a soft reset which is controlled by the firmware..

If any of the above reset sources issues a backup domain reset signal, the backup domain will be reset.

# 5.4. Power on Sequence

In general, there are two scenarios for UC6226 power supply: to use the internal DC/DC, or bypass the internal DC/DC. The RTC region and VDD\_IO region are independent of the main power supply, and the power-on sequences do not affect or depend on each other.

It should be noted that after UC6226 is powered on, a start-up time of more than 230ms must be guaranteed. If the power is cut off in less than 230ms, the chip may work abnormally and V\_BCKP may consume more power.

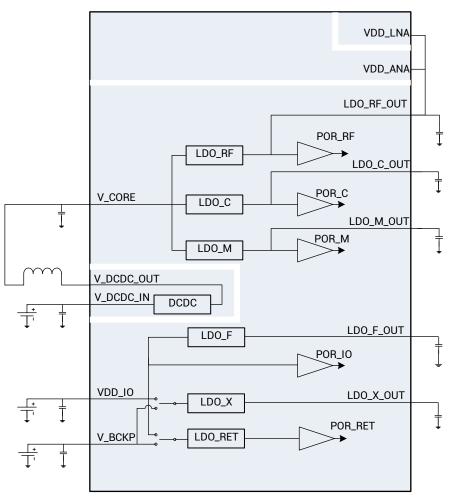

## 5.4.1. DC/DC Power-on and Sequence

Figure 5-1 DC/DC power-on and sequence

With the internal DC/DC, the supply efficiency is maximized. The main supply is connected to V\_DCDC\_IN pin, which is independent with VDD\_IO.

The power on time for main supply and the VDD\_IO should be shorter than 10ms and the power supply ramp should be monotonic. But there is no sequence requirement between the main supply and the VDD\_IO. However, the missing of any of these two supplies will keep the main circuit in reset state.

When V\_BCKP continues to power, the status of the main supply or VDD\_IO does not affect the status of RTC region.

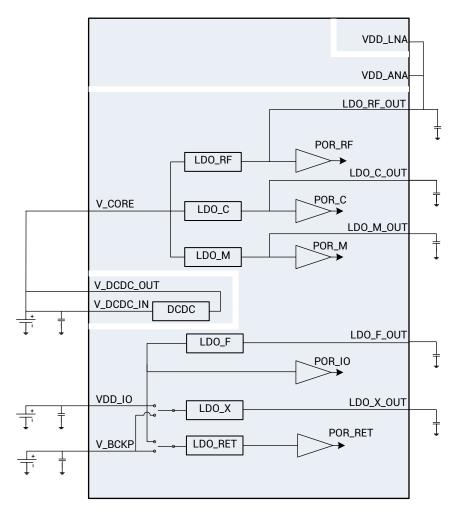

## 5.4.2. DC/DC Bypass Power-on and Sequence

Figure 5-2 DC/DC bypass power-on and sequence (Main Supply is 1.2V ~ 1.98V)

Without the internal DC/DC, the number and cost of external components are minimized. In this case, the main supply is connected to V\_DCDC\_IN, V\_DCDC\_OUT and V\_CORE pins, which is independent with VDD\_IO.

Please pay attention that the allowed input voltage of main supply in this mode is limited to 1.2V

-1.98V. The supply voltage higher than 1.98V will cause permanent damage of UC6226 chip.

The power on time for main supply and the VDD\_IO should be shorter than 10ms and the power supply ramp should be monotonic. There is no sequence requirement for the main supply and the VDD\_IO. However, the missing of any of these two supplies will keep the chip in reset state.

When V\_BCKP continues to power, the status of the main supply or VDD\_IO does not affect the status of RTC region.

# 5.4.3. Power on Sequence for Backup Region

The Backup region is powered by the output of an internal power switch, which switches between the IO supply from VDD\_IO pin and the backup supply from V\_BCKP pin. In order to minimize the backup battery consumption, only when the VDD\_IO is powered off does the switch change to V\_BCKP supply.

If neither VDD\_IO nor V\_BCKP is powered, the backup region does not work. If any one of pins is supplied, the backup region will be reset and soon start to be functional.

# 6. Pin Definitions

# 6.1. Pin Distribution

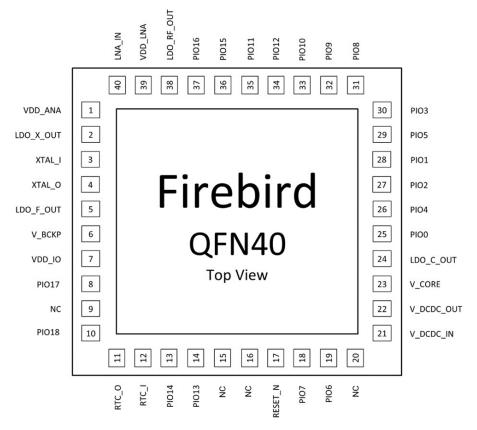

Figure 6-1 QFN40 pin diagram

# 6.2. Pin Description

#### Table 6-1 Description of QFN40 Power Supply Pin

| Name       | Pin | Power Domain | Description                      |

|------------|-----|--------------|----------------------------------|

| V_DCDC_IN  | 21  | DC/DC        | DC/DC input                      |

| V_DCDC_OUT | 22  | DC/DC        | DC/DC output                     |

| V_CORE     | 23  | Core         | Core supply                      |

| V_BCKP     | 6   | Backup       | Backup cell supply               |

| VDD_IO     | 7   | 10           | I/O, TCXO and Flash power supply |

| VDD_ANA    | 1   | Core/RF      | Power supply of analog section   |

| VDD_LNA    | 39  | Core/RF      | LNA power supply                 |

| LDO_RF_OUT | 38  | Core/RF      | RF power output                  |

| LDO_C_OUT  | 24  | Core/Logic   | Core power output                |

| LDO_X_OUT  | 2   | Clock        | TCXO/crystal power output        |

| LDO_F_OUT  | 5   | Flash        | Flash power output               |

| PADDLE     | 0   |              | Ground                           |

#### Table 6-2 Description of QFN40 Analog Pin

| Name    | Pin | Power Domain | Description                                            |

|---------|-----|--------------|--------------------------------------------------------|